- PCI や PCI-X 等のインタフェースから PCI Express へ速やかに移行できます。

PCI Express 機器の開発には、PCI Express 規格の理解に加えて、用途に応じ

た適切なデバイスの選定や、基板設計などにノウハウが必要となります。PCI

Express 機器を初めて開発する場合には、これらのノウハウの蓄積にそれなり

の期間を要する場合があります。そもそも PCI Express の膨大な規格のうち、

どの部分をどこまで理解する必要があるかを把握するまでにも相当の時間を要

することが予想されます。

本パッケージに含まれるコンサルティングと技術サポートをご利用いただくと、

設計方針の選定やノウハウの蓄積に要する期間を大幅に短縮できます。

- 必須な機能のみを実装することで、回路規模を抑えられます。

PCI Express 規格では、必ずしもすべての機器に必要とは言えない多くの機能

が、実装必須と規定されています (電力管理、動的レーン幅変更、詳細なエラー

報告等)。PCI Express 規格に準拠した一般的な IP コアにはこれらの機能

がすべて搭載されているため、場合によっては不要な機能に回路資源を割かね

ばならない状況が発生します。

GPCIe は必要最小限の回路で最高の実効転送性能を得られるように最適化され

た IP コアです。PCI Express 規格に完全には準拠しておらず、また完全準拠

を目標としていません。基本的な機能以外の機能は、用途に応じて追加実装す

る方式を採ります。このため PCI Express 規格に完全準拠させる場合に比べ、

回路消費を抑えることが可能です。

|

|

- 付属のソースコードを使用してユーザ独自の改変が可能です。

本パッケージには GPCIe のソースコード (VHDL で記述) が付属しますので、

回路の一部を流用、あるいは参考に独自の改変を施し、独自のインタフェース

を開発することが可能です。そのようなインタフェースの一例として、本パッ

ケージには当社独自規格 GLink の IP が付属します。

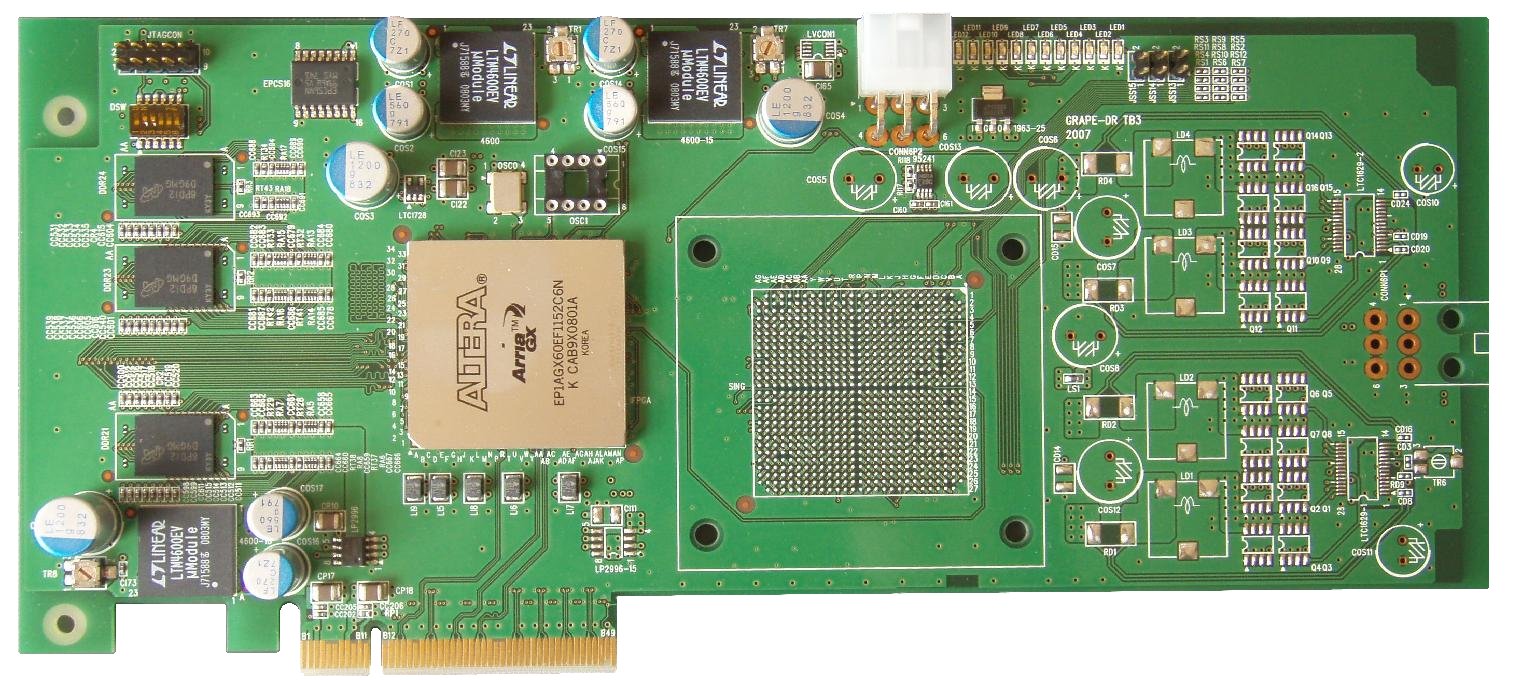

またソースコードにアクセスできるため、FPGA 組み込み型のロジックアナラ

イザ (Altera 社 SignalTapII、Xilinx 社 ChipScope 等) を用いてIP コア内

部の挙動を観測することが可能です。例えば Flow Control バッファの利用率

や送受信用ステートマシンの状態を観測できます。観測結果は最適なリソース

配分や通信ボトルネックの理解に役立つでしょう。

- 実効転送性能を極限までピーク性能に近づけられます。

GPCIe は実効性能を重視して設計されており、そのまま使用するだけでも低レ

イテンシ、高スループットの実効性能が得られます (参考:実測性能) が、接続先の機器の特性に合わせたカスタ

マイズによってより一層の性能向上を得られるように、数多くのカスタマイズ

用パラメタが generic parameter として用意されています。たとえば 合計

12 種 (upstream/downstream, Posted/Non-Posted/Completion, header/body)

の Flow Control バッファ サイズを generic parameter によって個別に調整可能です。

さらに高度な最適化が必要な場合には、本パッケージに付属する GPCIe のソー

スコードにユーザ自身が手を加えることも可能です。

|