製品情報 : 科学技術計算向け加速システム GRAPE-9

|

|

|

|

| 写真はプロセッサカードを 8 枚搭載した GRAPE-9 model5000/8 です。 |

プロセッサカード (表) |

プロセッサカード (裏) |

主な特長

-

当社開発の科学技術計算向けパイプライン回路を搭載した加速システムです。

- 目的に応じた演算をソフトウェア (プログラム) ではなくハードウェア

(パイプライン回路) によって実現するため、演算性能当りの消費電力を低く抑えられます

(典型的には NVIDIA 社 GTX Titan に比べ 1/4 程度)。

- 並列度が比較的低くても (〜数百) ピーク性能に近い実効性能が得られます。

惑星形成、球状星団等、高密度粒子系シミュレーションにおいて、

実用的な規模 (粒子数〜10k) でピーク性能に近い実効性能が得られます。

- ユーザはユーザライブラリを通じて、全プロセッサチップを 1 つのデバイスとして扱えます。

複数のプロセッサチップを並列動作させるために MPI 等を用いて並列コードを記述する必要はありません。

- パイプライン回路は 16 個のプロセッサチップ (Altera 社製 FPGA) に集積されており、

用途に応じて書き換えが可能です。

- 当社にて動作検証済みの 2 種類の重力相互作用パイプライン

(GRAPE-6 相当および GRAPE-5 相当) が付属します。

ユーザライブラリ (C, FORTRAN) は従来機 (GRAPE-5, GRAPE-6, GRAPE-7, GRAPE-DR, GRAPE-9 model800)

と互換ですので、現在それらの機種をお使いのユーザは、計算コードをそのまま流用できます。

- パイプライン開発ユーティリティ PGPG2

を用い、ユーザ自身でパイプラインを設計できます。

仕様

| プロセッサチップ |

Altera CycloneV GX (5CGXFC9) 16 個 |

| ホストインターフェイス |

Gen2 16 レーン PCI Express (最大 2 本)。各プロセッサチップには PCI Express スイッチデバイス (PEX8696) を経由して

透過的に Gen1 4 レーン PCI Express で接続 |

| 付属するパイプライン |

重力相互作用計算(GRAPE-6相当) 約 3 Tflops peak (見込み)

重力相互作用計算(GRAPE-5相当) 約 12 Tflops peak (見込み)

|

| オンボードメモリ |

計 16 GB (各プロセッサチップに DDR2 メモリ 1GB を接続) |

| 給電 |

100-220V AC |

| 消費電力(最大) |

約 300 W |

| その他 |

- 電源ユニット、冷却ファンを装備した専用筐体に収納。

専用筐体から Gen2 16 レーン PCI Express External Cable を介してホスト計算機の

PCI Express スロットへ接続。

- ホスト計算機上のデバイスドライバやデータ転送ライブラリから

は 16 個のプロセッサチップがそれぞれ別個の デバイスとして扱わ

れる。ユーザはユーザライブラリを通じて、16 個のプロセッサチッ

プを 16 個の独立したデバイスとして扱うことも、また 1 つのデバ

イスとして扱うことも可能。

- プロセッサチップの内部回路はホスト計算機から書き換え可能。

|

ソフトウェア、データ、資料

- GRAPE ソフトウェアパッケージ :

デバイスドライバ等の基本ソフトウェアと GRAPE-5/6/7/DR 互換の重力計算ライブラリ。

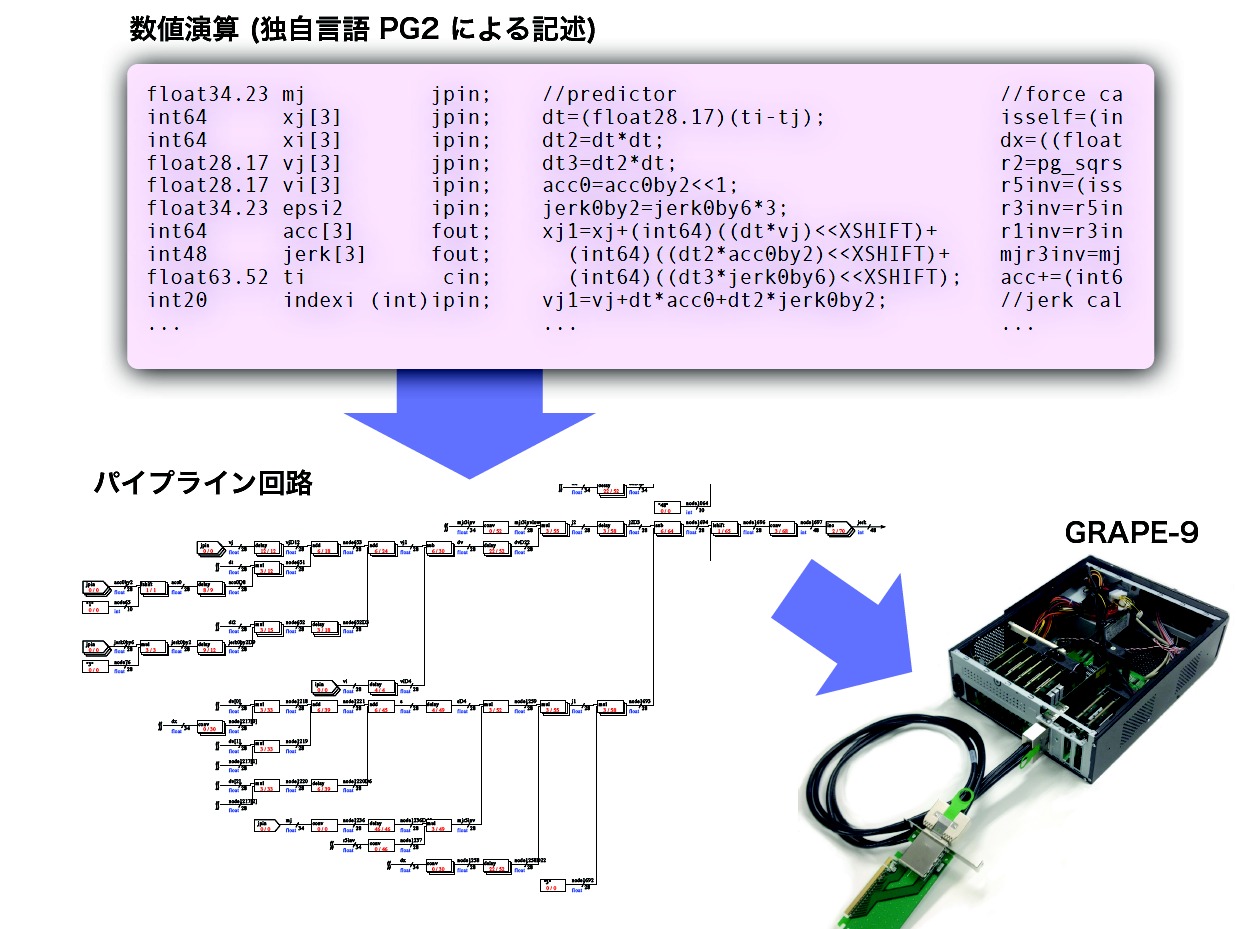

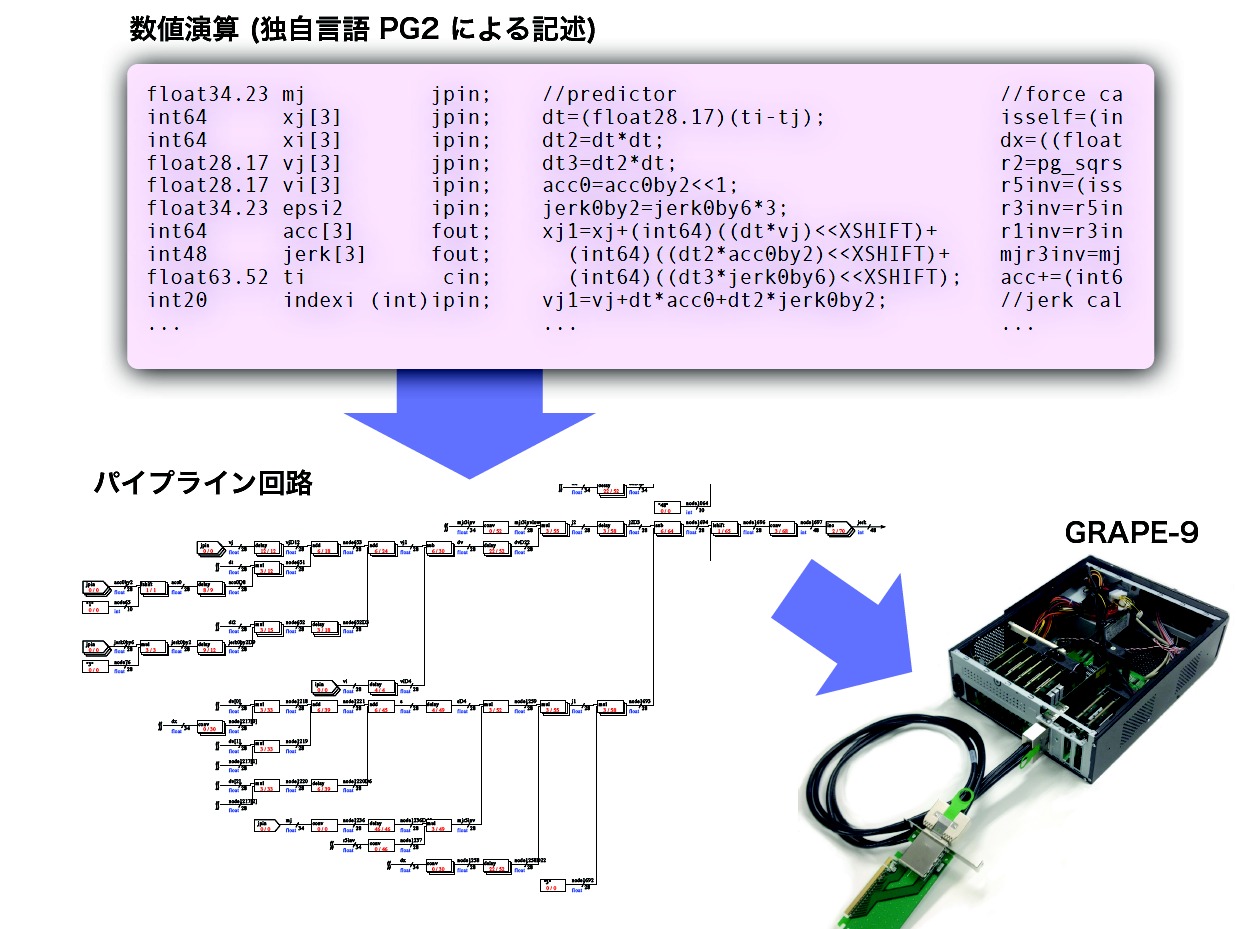

- 数値演算回路設計ソフトウェア PGPG2 (別売) :

ユーザ自身でプロセッサチップ内のパイプラインを設計するためのソフトウェア。

実測性能

準備中

標準価格

- GRAPE-9 model5000 (プロセッサチップを 16 個搭載) : 2,560,000 円 (税抜)

- GRAPE-9 model5000/8 (プロセッサチップを 8 個搭載) : 1,280,000 円 (税抜)

2 年間の技術サポート付属。

当社にてホスト計算機に GRAPE-9、ソフトウェア環境 (ドライバ、ライブラリ

等) 等をインストールして動作テストを行い、即座に使用できるよう設定した

状態で納品いたします。ホスト計算機のカスタマイズ (CPU、チップセット、メ

モリサイズ、ディスクサイズ、ケース形状等) も承っております。詳しくはご

相談ください。

PGPG2 (Pipeline Generator for Programmable GRAPE, generation 2注1) は、

C 言語に似た独自の高級言語で記述した数値演算から、その演算を実行するためのパイプライン回路を

生成するソフトウェアです。生成された回路は GRAPE-9 のプロセッサチップに書き込んで使用します。

- 独自の高級言語 PG2 による記述から、ハードウェア記述言語 VHDL

で記述されたパイプライン回路を自動生成します。典型的なケースでは、

PG2 による記述 10 〜 100 行をもとに VHDL による記述 1000 〜10000

行が生成されます。

- 生成された回路は Altera 社の論理合成ツール Quartus II を用いて合成できます。

合成された回路は GRAPE-9 上のプロセッサチップに書き込んで使用します。

- 回路をホスト計算機上のアプリケーションから利用するためのライブラリとヘッダファイル、

回路のブロック図なども自動生成されます。

著作権

下記について、著作権は当社に帰属します。

- 製品本体

- 製品を用いて出力した生成物のうち、VHDL ソース注2、

ネットリスト、ビットストリームデータ

利用許諾

- 製品、および製品を用いて出力した生成物のうち VHDL ソース、ネットリストに関して :

GRAPE-9 以外のハードウェアでの利用を目的とした改変を禁じます。

また複製物あるいは改変物の全部あるいは一部を、

製品を購入したユーザ以外に販売あるいは配布することを禁じます。

- 製品に関して : 購入したユーザが使用する限りにおいて、複製の作成を許可します。

製品を購入したユーザが使用する限りにおいて、

製品をインストールする PC の台数に制限はありません。

- 製品を用いて出力した生成物のうち、ビットストリームデータ (例: .sof ファイル、.pof ファイル)

に関して : 販売および配布を許可します。

上記の条件を満たさない利用については別途ご相談ください

(例: GRAPE-9 以外のハードウェアでの利用を目的とした改変を加える、

製品の改変物の販売、配布を行う)。

標準価格

238,000 円 (税抜)

ご希望の数値演算記述と、そこから生成されたパイプライン回路を各 1 つずつ、

サンプルとして提供いたします。

2 年間の技術サポート付属。

|

|

|

|

| GRAPE-9 model800 |

プロセッサカード (表) |

プロセッサカード (裏) |

主な特長

-

当社開発の科学技術計算向けパイプライン回路を搭載した加速システムです。

- 目的に応じた演算をソフトウェア (プログラム) ではなくハードウェア

(パイプライン回路) によって実現するため、演算性能当りの消費電力を低く抑えられます

(典型的には NVIDIA 社 GTX 580 に比べ 1/5 程度)。

また比較的並列度が低くても (数十〜数百)、ピーク性能に近い実効性能が得られます。

- ユーザはユーザライブラリを通じて、全プロセッサチップを 1 つのデバイスとして扱えます。

複数のプロセッサチップを並列動作させるために並列コードを記述する必要はありません。

- パイプライン回路は 8 個のプロセッサチップ (Altera 社製 FPGA) に集積されており、

用途に応じて書き換えが可能です。

- 当社にて動作検証済みの 2 種類の重力相互作用パイプライン

(GRAPE-6 相当および GRAPE-5 相当) が付属します。

ユーザライブラリ (C, FORTRAN) は従来機 (GRAPE-5, GRAPE-6, GRAPE-7, GRAPE-DR)

と互換ですので、現在それらの機種をお使いのユーザは、計算コードをそのまま流用できます。

- パイプライン開発ユーティリティ PGPG2

を用い、ユーザ自身でパイプラインを設計できます。

仕様

| プロセッサチップ |

Altera CycloneIV GX (EP4CGX150) 8 個 |

| ホストインターフェイス |

Gen2 16 レーン PCI Express。各プロセッサチップには PCI Express スイッチデバイス (PEX8696) を経由して

透過的に Gen1 4 レーン PCI Express で接続 |

| 動作確認済パイプライン |

重力相互作用計算(GRAPE-6相当) 80 本 149MHz 動作 (680 Gflops peak)

重力相互作用計算(GRAPE-5相当) 448 本 186MHz 動作 (3.17 Tflops peak)

|

| オンボードメモリ |

計 16 GB (各プロセッサチップに DDR2 メモリ 2GB を接続) |

| 給電 |

100-220V AC |

| 消費電力(最大) |

約 150 W |

| その他 |

- 電源ユニット、冷却ファンを装備した専用筐体 (100 mm x 306 mm x 402 mm)に収納。

専用筐体から Gen2 16 レーン PCI Express External Cable を介してホスト計算機の

PCI Express スロットへ接続。

- ホスト計算機上のデバイスドライバやデータ転送ライブラリから

は 8 個のプロセッサチップがそれぞれ別個の デバイスとして扱わ

れる。ユーザはユーザライブラリを通じて、8 個のプロセッサチッ

プを 8 つの独立したデバイスとして扱うことも、また 1 つのデバ

イスとして扱うことも可能。

- プロセッサチップの内部回路はホスト計算機から書き換え可能。

|

ソフトウェア、データ、資料

- GRAPE ソフトウェアパッケージ :

デバイスドライバ等の基本ソフトウェアと GRAPE-5/6/7/DR 互換の重力計算ライブラリ。

- 数値演算回路設計ソフトウェア PGPG2 (別売) :

ユーザ自身でプロセッサチップ内のパイプラインを設計するためのソフトウェア。

実測性能

準備中

標準価格

800,000 円 (税抜)。

2 年間の技術サポート付属。

- 注1: PGPG2 は PGPG (Hamada et al.,

2005) をもとに、当社にて機能拡張を行ったユーティリティです。PGPG

のその他の機能拡張には PGR (Hamada

& Nakasato, 2005) があります。PGPG2 の採用した「高級言語による

パイプライン記述」の概念は、会津大学中里准教授によって提案されたもので

す (2006 年)。

- 注2: 製品の出力する VHDL ソースの一部には、

製品本体に含まれる VHDL ソースの複製が含まれます。

- お問合せは info@kfcr.jp まで。